WLP、WLCSP元件的焊點間距相當小,不同的焊墊設計也會左右焊點間的走線寬度限制,設計PCB時限制較多。

隨著晶圓級晶片尺寸封裝WLP、WLCSP,在微縮晶片的成效越來越顯著,在電子產品的使用現況也有持續增加的現象,但WLP、WLCSP雖然可以在封裝后晶片的尺寸可達到如同晶粒同等大小、具尺寸的絕佳優勢,但在封裝成品功能日趨復雜、接腳數目與設計要求越來越嚴苛,對

PCB設計即成為新的應用挑戰...

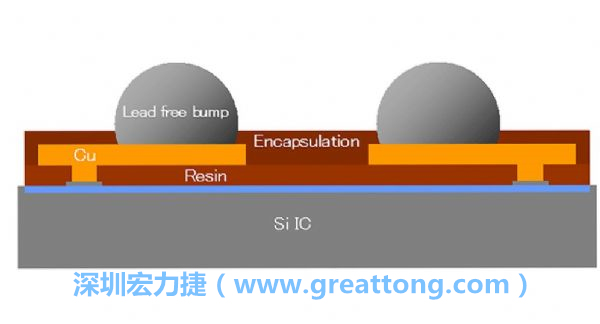

晶圓級晶片尺寸封裝WLP(Wafer Level Packaging)、WLCSP(Wafer Level Chip Scale Package),其實是積體電路的一種封裝方式,指的是在晶圓(Wafer)生產完成后直接于Wafer上進行封裝、測試程序,當封裝制作完成再進行切割成單個積體電路的封裝制作方式。

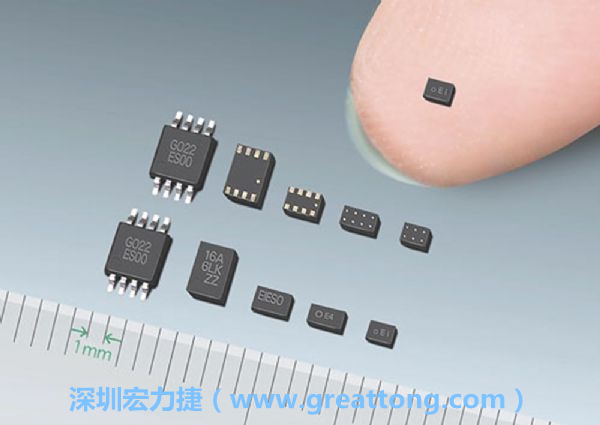

常規IC與WLP制作的封裝設計元件,尺寸有極大的差異,WLP僅需晶粒尺寸就有相同的電氣特性。

WLP為在晶圓階段即進行元件封裝,因此無常規IC的引腳、封裝體填膠等空間需求,元件尺寸可以做到晶粒大小,因此PCB設計挑戰更大。

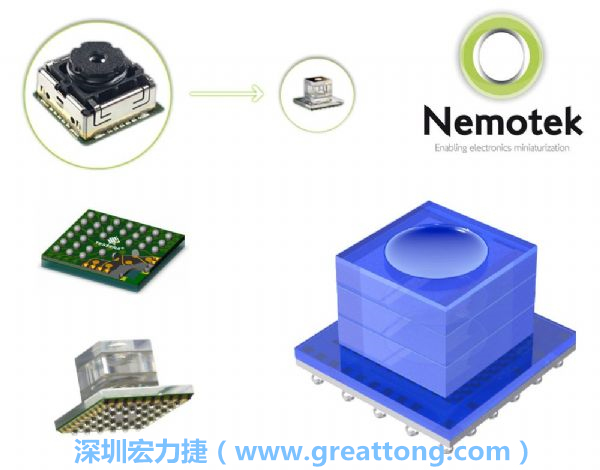

Nemotek利用WLP制作image sensor模組,搭配光學透鏡設計,可讓image sensor模組的占位面積大幅縮小,生產可用自動送料快速制作,節省產制成本。

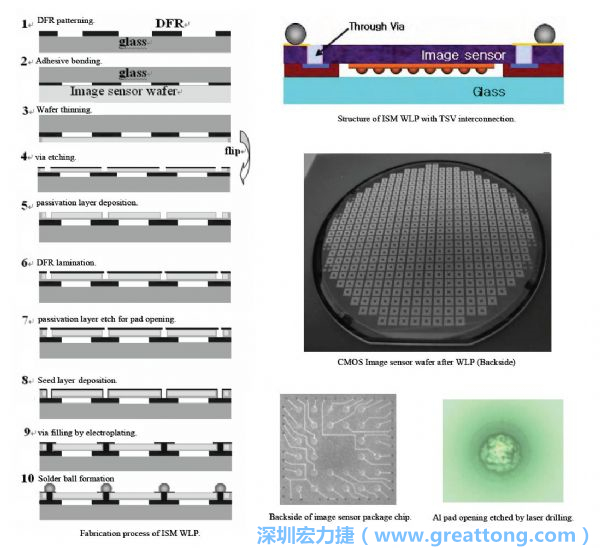

Samsung采用WLP形式制作的image sensor,直接利用晶圓級封裝大幅縮減元件尺寸,元件可做到極薄與最小占位面積。

WLP、WLCSP有別于晶圓切割成晶粒、再經由封裝中打線追加引腳的積體電路制作方式,正因為少了封裝的體積占用,WLP、WLCSP可以達到相同的IC應用功能,卻只要如同切割后晶粒大小的占位面積,而WLP、WLCSP制成單顆IC過程中,亦不用如同一般IC需進行打線、填膠,在發展小型化或超小型的微縮設計產品方案時,WLP、WLCSP封裝設計方式的IC應用,可以達到極佳的產品微縮效益,加上WLP、WLCSP元件本身具備極佳電性(因為少了打線與引腳),針對高速傳輸應用的元件使用效益更高,元件因可在晶圓上加工,也縮減了IC的繁瑣制程。

WLP、WLCSP體積小、重量輕

但問題來了,WLP、WLCSP雖然體積相當小,隨著常規IC的接腳數目越來越多,WLP、WLCSP形式封裝使用的球距要求趨于嚴苛,但對于電路設計所需要的電性,基本上跟一般IC所需的電性支援并無不同,但WLP、WLCSP的尺寸已經縮小到晶粒尺寸,加上PCB可與WLP、WLCSP連接的接點、線路都極小,在PCB的設計方案并不如一般IC應用方案來得輕松。

至于,采用行晶圓級封裝,目的是為了降低解決方案的成本與整體尺寸,但連帶的當導入晶圓級封裝后,PCB的成本勢必會因為采用行晶圓級封裝,必須進行對應的線路與打孔制程改善,讓PCB特性可以與WLP、WLCSP元件充分搭配,而不會出現連接上的問題。尤其在設計方案中使用了WLP、WLCSP后,PCB會變得更趨復雜,角色也會顯得較為重要,設計時需審慎規劃,避免PCB的質量導致終端產品出現穩定度問題。

當我們在進行載板設計時,基本上在現有的設計產品中,可用的載板面積已經越來越小,而工程師又得面對持續縮小的設計要求,例如,穿戴型的電子產品,如手表型、行動電話的電子電路,可使用的載板空間極度珍貴,而為了降低終端設計采用行的PCB面積,導入如WLP、WLCSP更小的IC封裝,已經是無法避免的設計趨勢。

在晶圓階段進行元件封裝 大幅節省載板占位面積

由于WLP、WLCSP封裝是直接建立「硅」基板上的封裝制程,IC基本上是不需使用焊線,對高頻元件來說可直接獲得更好的高頻電性,達到縮短周期時間效益,而因為封裝可以在晶圓廠完成,同時可節省封裝成本,但對于工程師來說,設計方案也必須朝向降低成本方向考量,要搭配WLP、WLCSP元件同時PCB成本也必須限制在一定程度范圍,必須注意權衡設計,或采用取線路布局對應。

一般來說,進行導入WLP、WLCSP元件,在執行PCB線路布局規劃前,工程師必須先取得WLP、WLCSP的占位面積(即封裝后尺寸),同時對WLP、WLCSP元件確認尺寸/接點誤差、接點間距等元件關鍵訊息,開始進行電路布局、處理元件擺位,即可利用取得的元件參數進行設計規劃,而因應WLP、WLCSP的尺寸與接點變得更小,還須考量適用IC接腳的焊墊設計方案。

PCB需針對SMD、NSMD形式做對應微調

可搭配WLP、WLCSP的焊墊類型,可以使用Solder Mask Defined(SMD)與Nonsolder Mask Defined(NSMD)。焊罩定義型SMD焊墊,其設計方式為利用焊罩定義焊球、將被焊接之焊墊面積,這種設計方案可以減少焊墊于焊接或除焊過程,可能被拉高的可能性,但SMD形式的缺點是,SMD減少了與錫球連接之銅表面的表面積,同時減少相鄰焊墊間的空間,這會讓焊墊間的走線寬度受限,也可能造成PCB的導通孔使用彈性。在多數設計方案中,較被常用的仍是SMD設計方案,因為SMD的焊墊可以有較佳的焊錫連接特性,在制作過程中可讓焊錫和焊墊整個結合在一起。

至于非焊罩定義型焊墊(NSMD),設計方法是利用銅進行焊錫凸塊焊接之焊墊面積定義,這種設計方案可提供更大的表面積,來使PCB與錫球進行連接,同時NSMD相較SMD設計形式,亦提供焊墊與焊墊間更大的絕緣間距,可允許更寬的焊墊間走線間距,對于PCB的導通孔的使用彈性更高,但NSMD若在進行焊接、除焊等操作過程很容易造成焊墊被拉高。

針對間距需特別考量

間距尺寸的考量也相當重要,尤其是PCB在采用行SMD或NSMD形式,不同的方案在預留的間距尺寸也會略有差異,而間距尺寸指的是錫球間的距離,此為兩個錫球的圓心距離,而間距尺寸越大,代表焊墊與焊墊之間可用來進行布線的線路空間越大。

對于0.5毫米的設計方案中,由于間距較大,提供更多的走線空間,或是設計時可以使用較寬、銅材料較多線路,這表示可在走線驅動更高的傳輸電流,絕緣距離也可以輕松完成設計。對于絕緣距離,一般需檢視所要求的設計規范,一般絕緣距離為3~3.5密爾(mil)。相較0.4毫米的間距寬度設計,就相對設計更為困難,因為可用的布線空間彈性限制更多,而可用的絕緣間距也會因為間距縮小而同時減少,這代表可在線路中使用的銅變少了,傳輸的驅動電流也會對應減少。

在PCB布線方面,因為WLP、WLCSP元件特性,可用的錫球間距相當小,基本上是無法使用機械開孔設備進行PCB開孔,因為機械開孔的孔徑過大,開孔過程也可能讓PCB上較薄的線路因為開孔過程誤差受損。而在有使用WLP、WLCSP元件的PCB,由于線路較緊密許多,也會改用成本較高的雷射鉆孔來處理導通孔(laser-drilled via)。

一般來說,只有在中、高單價的終端產品,才會使用高成本的雷射開孔PCB制作方案,而會用雷射開孔也會同時搭配多層板進行制作,成本會較四層板高許多,對于一些低成本應用方案,使用多層板、雷射開孔設計方案基本上是較為不劃算。而另一種相對不常見的設計方案,是采用行交錯錫球凸塊陣列(staggered bump array)之WLP元件,利用做在WLP晶片上使錫球交錯,讓產品開發者爭取更多可用空間來進行PCB線路布局。但事實上WLP搭配staggered bump array的成本相當高,同時,此方案必須在WLP、WLCSP元件進行開發時就同步進行考量,在元件制作難度較高,也會因此提高元件成本。

結語

晶圓級晶片尺寸封裝WLP、WLCSP元件,對于縮小終端產品尺寸具有極佳的改善效益,但換來的是PCB設計方案也必須同步升級,搭配高密度多層板、雷射開孔的精密制程進行開發,原本自IC元件省下的載板空間、元件成本,會部分轉嫁到PCB設計與后段的量產制作上,而采用行更小的元件,在產品后段的產線打件、加工或維修,也會造成部分較難施作的操作問題,這在進行相關設計前都必須一一考量。

WLP、WLCSP元件為晶圓級晶片尺寸封裝,最終IC的外觀、尺寸之封裝大小幾乎與晶片是相同的,晶圓級的晶片尺寸封裝優點相當多,像是元件尺寸大幅縮小,減少了常規IC應有的面積、厚度,元件的重量更輕,元件可利用更適應大量產線生產的自動化上料打件制作,可降低整體生產成本,甚至WLP、WLCSP元件本身針對高頻應用的電氣特性表現會更好,應用在需要輕量化、縮小體積的行動裝置,如手機、筆記型電腦、穿戴式智慧產品,都可以用來大幅縮減載板面積、產品重量的重要手段。WLP、WLCSP元件若可以在導入前即針對晶圓級封裝技術做更多整合,如搭配重新布線層技術、凸塊等改善WLP、WLCSP元件設計,可以讓WLP、WLCSP元件與PCB的搭配整合在設計上更為輕松。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料