對(duì)系統(tǒng)開發(fā)展設(shè)計(jì)工程師而言,要能同時(shí)兼顧IC設(shè)計(jì)、封裝與印刷電路板(PCB)系統(tǒng)層級(jí)的設(shè)計(jì),相當(dāng)困難,也需要花更多時(shí)間一一了解。這并不表示

PCB設(shè)計(jì)工程師能力不足,而是這三領(lǐng)域各有不同的專業(yè)知識(shí)--隔行如隔山--要能通盤了解并設(shè)計(jì)出初步的系統(tǒng),可能得花上一段時(shí)間。

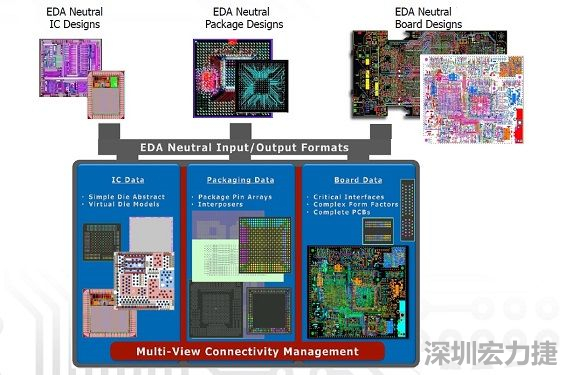

IC設(shè)計(jì)、封裝與PCB系統(tǒng)設(shè)計(jì)都有標(biāo)淮規(guī)范可依循,且業(yè)者都針對(duì)自己的「強(qiáng)項(xiàng)」推出設(shè)計(jì)工具,以方便設(shè)計(jì)者設(shè)計(jì)其系統(tǒng)。然而這樣的設(shè)計(jì)工具由于只針對(duì)IC設(shè)計(jì)進(jìn)行,因此PCB系統(tǒng)設(shè)計(jì)工程師在設(shè)計(jì)時(shí),仍須針對(duì)IC、封裝與PCB系統(tǒng)的接腳路徑進(jìn)行規(guī)劃,而IC設(shè)計(jì)與封裝領(lǐng)域?qū)CB系統(tǒng)設(shè)計(jì)工程師來說猶如一堵高墻,要讓每個(gè)階段的接腳路徑設(shè)計(jì)都順利完成,將曠日費(fèi)時(shí),產(chǎn)品上市時(shí)間將因而拉長(zhǎng)。

有鑒于此,Xpedition Package Integrator軟件流程,協(xié)助PCB設(shè)計(jì)工程師順利進(jìn)行系統(tǒng)設(shè)計(jì)。Xpedition Package Integrator可該解決方案可確保IC、封裝和PCB三者間接腳路徑的規(guī)劃是相符的,且其精簡(jiǎn)設(shè)計(jì)工具可以讓設(shè)計(jì)工程師在IC、封裝與PCB的接腳位置、走線方式,都可快速且輕松的完成。

采用虛擬晶片模型概念,實(shí)現(xiàn)IC到封裝協(xié)同優(yōu)化的PCB系統(tǒng)設(shè)計(jì)軟件,可加快設(shè)計(jì)時(shí)程。

換句話說,透過這種協(xié)同設(shè)計(jì)的方式,設(shè)計(jì)工程師只要在系統(tǒng)頁(yè)面上,簡(jiǎn)單的畫出各接腳間的走線方式,軟件就可迅速將呈現(xiàn)正確的走線與接腳對(duì)應(yīng),工程師無(wú)須在一團(tuán)混亂中,慢慢對(duì)應(yīng)、找尋IC到封裝、封裝到PCB正確的接腳與走線。

如此一來,不僅可以讓設(shè)計(jì)工程師快速優(yōu)化互連路徑,還可減少PCB所需的層數(shù),進(jìn)而降低封裝基底和 PCB成本。該設(shè)計(jì)軟件能實(shí)現(xiàn)這樣的便利性,是由于該軟件整合各家IC設(shè)計(jì)、封裝廠與PCB業(yè)者的產(chǎn)品相關(guān)資訊與檔案格式。

更重要的是,解決了PCB設(shè)計(jì)工程師遭遇的難題之后,設(shè)計(jì)工程師將可加速系統(tǒng)設(shè)計(jì)時(shí)間。就難度較低且簡(jiǎn)單的PCB系統(tǒng)設(shè)計(jì)為例,過去工程師平均得花兩周時(shí)才能完成設(shè)計(jì),而Xpedition Package Integrator軟件流程可將設(shè)計(jì)時(shí)間縮短至5~10分鐘。

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料